### **Chapter 1. Introduction to Flash Programming**

| Flash RAM and On-board Programming.                    | 1-2  |

|--------------------------------------------------------|------|

| Flash Programming Concepts                             | 1-3  |

| Flash Programming Tasks.                               | 1-4  |

| Embedded Programming Algorithms for Flash Devices      | 1-5  |

| Intel® Algorithms 1-5                                  |      |

| Intel® Automated Byte/Word Programming Algorithm 1-5   |      |

| Intel® Byte/Word Programming Flowchart 1-6             |      |

| Intel® Block Erase Algorithm 1-8                       |      |

| AMD® Algorithms                                        | 1-9  |

| The AMD® Embedded Program Algorithm                    |      |

| The AMD® Embedded Erase Algorithm                      |      |

| The Advantages and Limitations of On-board Programming | 1-13 |

| The Advantages of On-board Programming                 |      |

| Limitations of On-board Programming:                   |      |

|                                                        |      |

### Chapter 2. Design For On-board Programming

| On Board Programming                                |                 | 2-2             |

|-----------------------------------------------------|-----------------|-----------------|

| OBP: A Different Approach to Test Development       | 2-2             |                 |

| Planning for Flash On-board Programming             |                 | 2-3             |

| On-board Programming Design Considerations          | 2-3             |                 |

| Board Design Recommendations                        | 2-4             |                 |

| Disable Bi-directional Signals to Prevent Bus Cor   | nflicts 2-4     |                 |

| Disable Input Signals to Prevent Backdriving Dan    | nage 2-4        |                 |

| Provide Access to All I/O Signals                   | 2-5             |                 |

| Use System Power Supply Levels and Document<br>2-5  | t Operational V | V <sub>cc</sub> |

| Establish Direct Access to BSDL Signals             | 2-6             |                 |

| Provide Data Protection and Disabling Information   | n. 2-6          |                 |

| What Test Developers Need to Know                   |                 | 2-7             |

| What is a Flash Programming Test?                   | 2-7             |                 |

| Data Sources and Board Topologies Effect OBP        | 2-8             |                 |

| Board Topologies for On-board Programming           | 2-9             |                 |

| Individual Flash Devices Connected by Separate<br>9 | Data Busses     | 2-              |

| A Series of Flash Devices Connected to a Single     | Data Bus 2-     | -10             |

Table of Contents-1

| Multiple Flash Devices Connected to a Single Large Data Bu | is 2- |

|------------------------------------------------------------|-------|

| 11                                                         |       |

| Parallel Flash Programming With HP Throughput Multiplier   | 2-12  |

| Creating a Sample Design Document                          |       |

### Chapter 3. Flash70 Digital Tests

| What is a Flash Digital Test?           |      | 3-2  |

|-----------------------------------------|------|------|

| The Series 3 Flash Compiler             |      | 3-2  |

| Data Interpretation                     | 3-2  |      |

| Automatic Segment Removal               | 3-3  |      |

| Flash70                                 |      | 3-3  |

| The Flash70 Algorithm                   | 3-4  |      |

| Faster Tests with the Flash70 Algorithm | 3-4  |      |

| Obtaining 12MHz Speed on 6MHz cards     | 3-7  |      |

| Hardware Waits                          | 3-10 |      |

| Data Blocks                             |      | 3-11 |

### Chapter 4. Data Sources for Flash Programming

| Overview                                                 | 4-1 |

|----------------------------------------------------------|-----|

| Data Blocks and OBP                                      | 4-2 |

| Using Data Blocks for Flash Programming 4-2              | 2   |

| Data Block Example Using a Motorola S-record 4-3         | 3   |

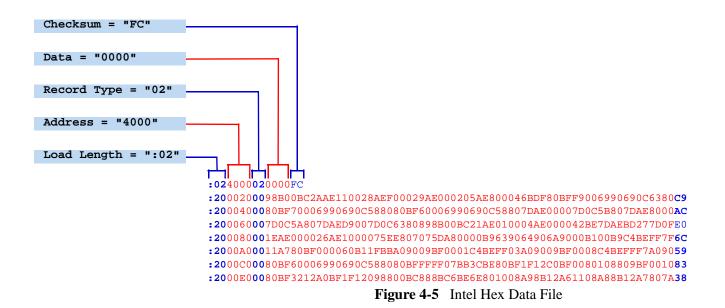

| Data Block Example Using an Intel Hexademical Record 4-3 | 3   |

| Formatted Records                                        | 4-4 |

| Motorola S-Records                                       | 4-4 |

| Record Types 4-5                                         | 5   |

| Start Record 4-5                                         | 5   |

| Data Record 4-6                                          | 3   |

| End Record                                               | 3   |

| Motorola S-Record Example                                | 7   |

| Structure of a Motorola S-Record 4-8                     | 3   |

| Intel Hexadecimal Records                                | 4-9 |

| Record Types 4-10                                        | )   |

| Data Record 4-11                                         | I   |

| End Record 4-11                                          | I   |

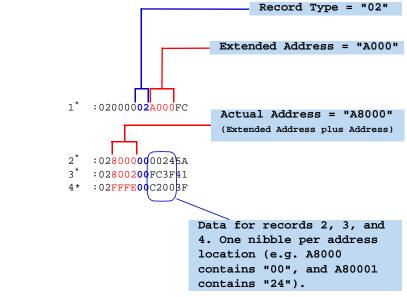

| Extended Segment Address Record 4-1                      | I   |

| Start Segment Address Record 4-11                        | 1   |

| Extended Linear Address Record                           | 2   |

| Start Linear Address Record                   | 4-12 |      |

|-----------------------------------------------|------|------|

| Intel Hex Record Example                      | 4-12 |      |

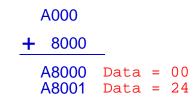

| Extended Segment Record Example               | 4-14 |      |

| General Data Block Usage                      |      | 4-16 |

| Testing Single-Byte Devices with Data Records |      |      |

| Testing multibyte Devices with Data Records   | 4-20 |      |

### Chapter 5. VCL Syntax for Flash OBP

| Overview                                                     | 5-1  |

|--------------------------------------------------------------|------|

| VCL Syntax in Flash Digital Tests                            | 5-2  |

| The Structure of a VCL Test                                  |      |

| Declaration section 5-2                                      |      |

| Timing section 5-2                                           |      |

| Vector Definition section                                    |      |

| Vector Execution section 5-3                                 |      |

| Placing Flash VCL Statements in a Test                       | 5-3  |

| VCL Statements in the Declaration Section of a Test 5-3      |      |

| Example Declaration Section for a Flash Test 5-4             |      |

| Description of Declaration Statements                        |      |

| flash                                                        |      |

| generate static test                                         |      |

| family 5-6                                                   |      |

| dynamic 5-6                                                  |      |

| Flash VCL Statements in the Definition Section of a Test 5-6 |      |

| Example Definition Section of a Flash Test 5-7               |      |

| Description of Definition Statements 5-8                     |      |

| file                                                         |      |

| file statement option                                        |      |

| Flash VCL Statements in the Execution Section of a Test 5-8  |      |

| Description of Flash VCL Execution Statements 5-10           |      |

| segment                                                      |      |

| repeat 5-11                                                  |      |

| execute and drive 5-11                                       |      |

| next                                                         |      |

| Syntax to Inhibit Flash70 Algorithm                          | 5-13 |

| Turning off the Flash70 Algorithm                            |      |

| Turning off All Flash Features                               |      |

| Turning off Limited Addressing                               |      |

| Turning off Segment Removal 5-13                             |      |

| Turning off Data Removal 5-14                                |      |

| File Statement Options          | 5-14 |

|---------------------------------|------|

| Default 5-15                    |      |

| "reuse" Data Modifier 5-16      |      |

| "unused" Data Modifier          |      |

| "user" Data Modifier 5-17       |      |

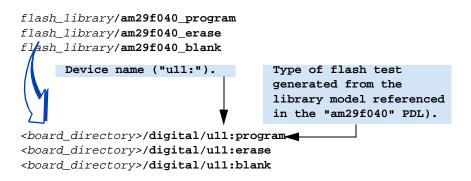

| 28f160 "u8:program" VCL Example | 5-18 |

### **Chapter 6. Generating Flash Digital Tests**

| Overview                                                         |             | 6-2  |

|------------------------------------------------------------------|-------------|------|

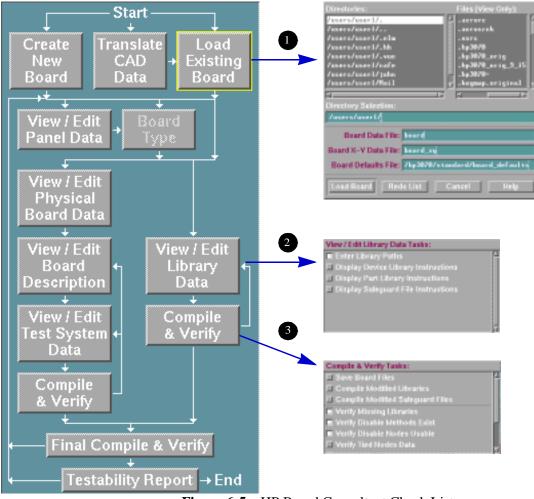

| Flash Test Development Tasks                                     |             | 6-3  |

| Section One: Flash OBP Programming Steps                         |             | 6-5  |

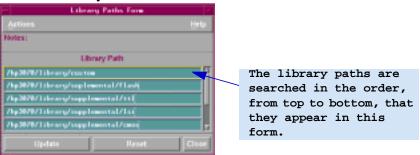

| Locating Flash PDL and Test Directories.                         |             | 6-7  |

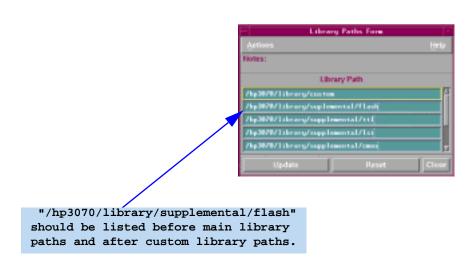

| /hp3070/libraries/supplemental/flash                             | 6-7         |      |

| /hp3070/boards/board_directory/digital                           | 6-7         |      |

| OBP Production Programming Task Flow                             | 6-8         |      |

| Flash Programming Test Flow                                      | 6-9         |      |

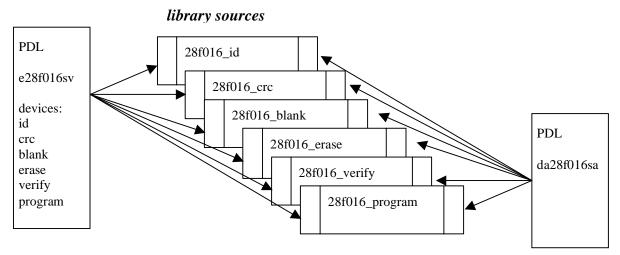

| Using HP 3070 Libraries to Develop Flash Tests6                  | 6-10        |      |

| Part Description Library Structure                               | 5-10        |      |

| PDL's Features                                                   | 5-11        |      |

| Library Structure                                                | 5-11        |      |

| IPG, PDLs, and Flash Test Library Models                         | 5-11        |      |

| Section Two: Steps to Developing Flash Digital Tests             | 6           | -13  |

| Step 1: Configuring the board 'config' file                      | 5-13        |      |

| Step 2: Verifying IPG Test Generation                            | 5-14        |      |

| Step 3: Running HP Test Consultant                               | 6-17        |      |

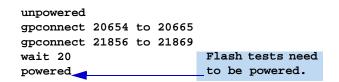

| Power Voltage Considerations                                     | 5-20        |      |

| Step 4: Modifying the 'testplan'                                 | 5-21        |      |

| Modifying the "testplan" for Panel or Throughput Multipl<br>6-22 | ier Topolog | jies |

| Other "testplan" considerations                                  |             |      |

| Section Three: Flash Tests and Existing Fixtures                 |             | -24  |

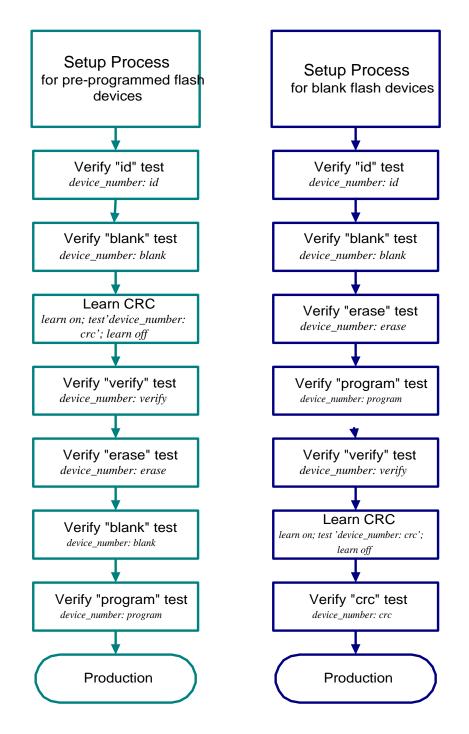

| Set Up A Flash Test Suite to Validate Your Test                  | 6           | -28  |

### **Chapter 7. Validating Tests for Production**

| Overview                            | 7-2 |

|-------------------------------------|-----|

| Task Flow for Testing OBP Libraries | 7-2 |

| Setup Process Task Flow             |     |

| Using IPG Generated Flash Tests to Setup OBP 7-                | •4 |

|----------------------------------------------------------------|----|

| The 'id' test                                                  |    |

| The 'blank' test                                               |    |

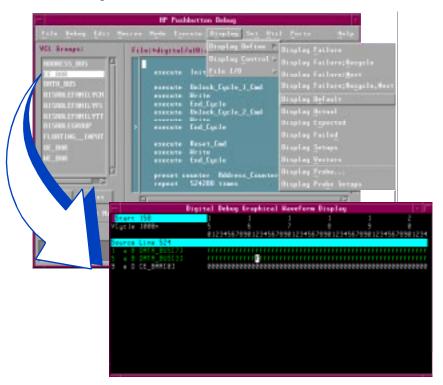

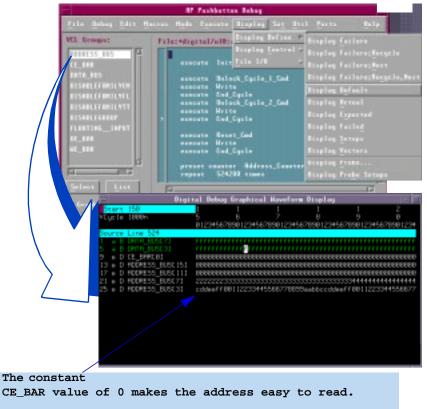

| Evaluating Device Data With Pushbutton Debug 7-7               |    |

| Displaying Accurate Addresses by Adding Extra Control Lines 7- | 9  |

| Displaying Accurate Addresses With the New Display Group 7-10  | )  |

| The 'crc' test                                                 |    |

| The 'verify' test                                              |    |

| The 'erase' test                                               |    |

| Verifying an Erased Device With the 'blank' test               |    |

| The 'program' test                                             |    |

| Troubleshooting a Failing "program" Test 7-16                  |    |

| Expanding the Test to the Full Memory Size of the Device 7-17  |    |

| Obtaining Speed Improvements with Flash70 7-18                 |    |

| Notes about Debug with Dynamic Vectors                         |    |

| Notes About Debugging With Flash70                             |    |

| Verifying that Programmed Data is Correct 7-21                 |    |

| Correcting Reversed Data Bits                                  |    |

| Address Misalignment                                           |    |

| Data Addressing for Data Records Larger Than 8 bits 7-24       |    |

| Addressing Data Modifiers                                      |    |

### Chapter 8. Series and Parallel Programming

| Series Flash Topology Cluster Test Programming Model                | 8-2 |

|---------------------------------------------------------------------|-----|

| Parallel Topology Cluster Test Programming Model                    | 8-5 |

| Performing a Parallel Test 8-5                                      |     |

| Add New Data Blocks to Reference Separate Files for Each Device 8-6 | 5   |

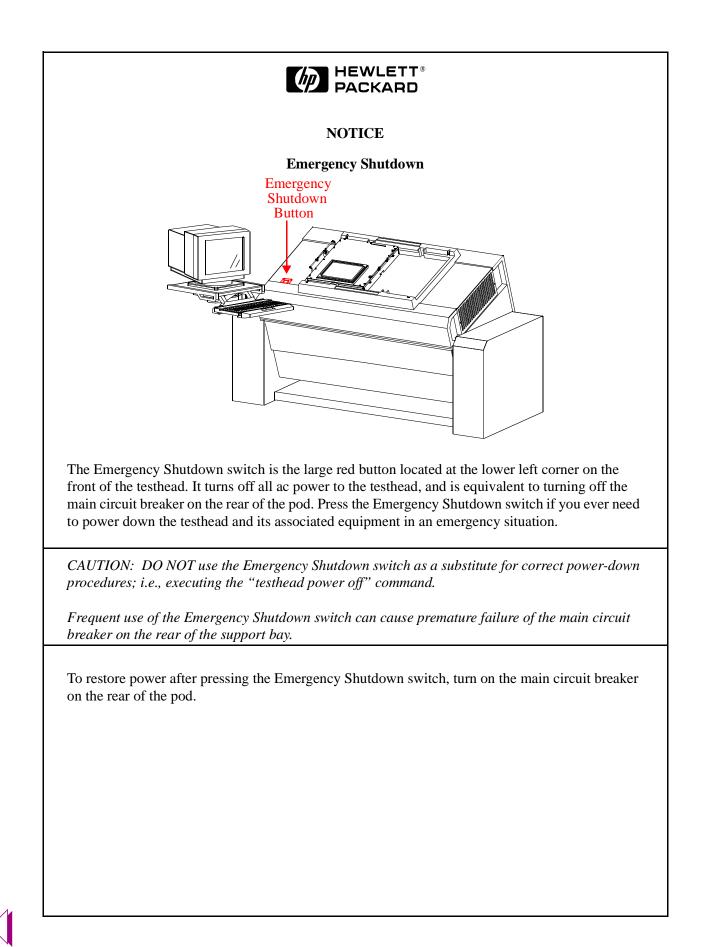

#### NOTICE

This manual is provided "as is" and is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein, nor for direct, indirect, general, special, incidental or consequential damages in connection with the furnishing, performance, or use of this material.

#### Copyright © 1985-1998, Hewlett-Packard Company.

## The XWD i/o and GIF output routines are derived from Jef Poskanzer's PBMplus package: © Copyright by Jef Poskanzer 1989

#### Printed in U.S.A.

#### **U.S.** Government Restricted Rights

The Software and Documentation have been developed entirely at private expense. They are delivered and licensed as "commercial computer software" as defined in DFARS 252.227-7013 (Oct 1988), DFARS 252.211-7015 (May 1991) or DFARS 252.227-7014 (Jun 1995), as a "commercial item" as defined in FAR 2.101(a), or as "Restricted computer software" as defined in FAR 52.227-19 (Jun 1987) (or any equivalent agency regulation or contract clause), whichever is applicable. You have only those rights provided for such Software and Documentation by the applicable FAR or DFARS clause or the HP standard software agreement for the product involved.

#### Insulation Rating for Wires Connected to the System

Use only external wiring with insulation rated for the maximum voltage (Vrms, Vpk or Vdc) and temperature to which the wire may be subjected in a fault condition.

Example: The system is connected to a source whose output is set at 50Vrms. The source could be set for as high as 300Vrms, intentionally or unintentionally. Therefore, the external wiring connected between this source and the system must be rated for 300Vrms.

#

#### WARRANTY

1. HP warrants HP hardware, accessories and supplies against defects in materials and workmanship for the period of one year. If HP receives notice of such defects during the warranty period, HP will, at its option, either repair or replace products which prove to be defective. Replacement products may be either new or like-new.

2. HP warrants that HP software will not fail to execute its programming instructions, for the period of one year, due to defects in material or workmanship when properly installed and used. If HP receives notice of defects during the warranty period, HP will replace software media which does not execute its programming instructions due to such defects.

3. HP does not warrant that the operation of HP products will be uninterrupted or error free. If HP is unable, within a reasonable time, to repair or replace any product to a condition as warranted, customer will be entitled to a refund of the purchase price upon prompt return of the product to HP.

4. HP products may contain remanufactured parts equivalent to new in performance or may have been subject to incidental use.

5. The warranty period begins on the date of delivery or on the date of installation if installed by HP. If customer schedules or delays HP installation more than 30 days after delivery, warranty begins on the 31st day from delivery.

6. Warranty does not apply to defects resulting from (a) improper or inadequate maintenance or calibration, (b) software, interfacing, parts or supplies not supplied by HP, (c) unauthorized modification or misuse, (d) operation outside the published environmental specifications for the product, or (e) improper site preparation or maintenance.

7. TO THE EXTENT ALLOWED BY LOCAL LAW, THE ABOVE WARRANTIES ARE EXCLUSIVE AND NO OTHER WARRANTY OR CONDITION, WHETHER WRITTEN OR ORAL, IS EXPRESSED OR IMPLIED AND HP SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY, SATISFACTORY QUALITY, AND FITNESS FOR A PARTICULAR PURPOSE.

8. HP will be liable for damage to tangible property per incident up to the greater of \$300,000 or the actual amount paid for the product that is the subject of the claim, and for damages for bodily injury or death, to the extent that all such damages are determined by a court of competent jurisdiction to have been directly caused by a defective HP Product.

9. TO THE EXTENT ALLOWED BY LOCAL LAW, THE REMEDIES IN THIS WARRANTY STATEMENT ARE CUSTOMER'S SOLE AND EXCLUSIVE REMEDIES. EXCEPT AS INDICATED ABOVE, IN NO EVENT WILL HP OR ITS SUPPLIERS BE LIABLE FOR LOSS OF DATA OR FOR DIRECT, SPECIAL, INCIDENTAL, CONSEQUENTIAL (INCLUDING LOST PROFIT OR DATA), OR OTHER DAMAGE WHETHER BASED IN CONTRACT, TORT, OR OTHERWISE.

FOR CONSUMER TRANSACTIONS IN AUSTRALIA AND NEW ZEALAND: THE WARRANTY TERMS CONTAINED IN THIS STATEMENT, EXCEPT TO THE EXTENT LAWFULLY PERMITTED, DO NOT EXCLUDE, RESTRICT OR MODIFY AND ARE IN ADDITION TO THE MANDATORY STATUTORY RIGHTS APPLICABLE TO THE SALE OF THIS PRODUCT TO YOU.

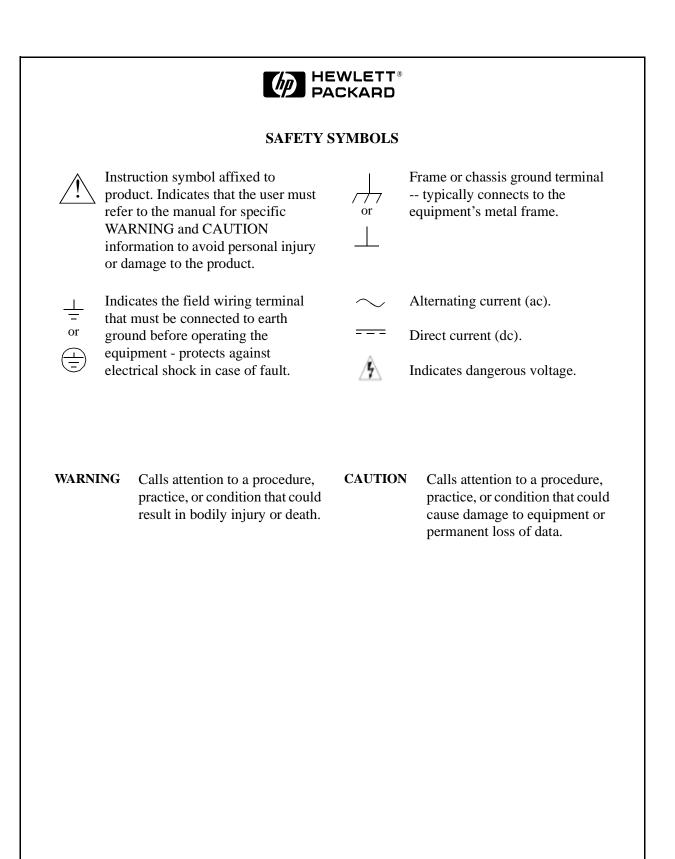

#### USER SAFETY SYMBOLS

These symbols are used on labels on various places on the testhead.

WARNING - Do not operate the testhead if you can see this symbol. It means that hazards exist because the safety shroud is not installed. These hazards include pinched fingers from pulling down a test fixture and electrical shock if HP Performance Port is installed.

WARNING - Keep your hands away from the indicated areas of the testhead to avoid pinched fingers when rotating the testhead.

WARNING - Do not rotate the testhead past 65 degrees with a fixture installed, or the fixture could fall off the testhead, causing personal injury.

#### WARNINGS

The following general safety precautions must be observed during all phases of operation, service, and repair of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of this product. Hewlett-Packard Company assumes no liability for the Customer's failure to comply with these requirements.

**Ground the Equipment:** For Safety Class I equipment (equipment having a protective earth terminal), an uninterruptable safety earth ground must be provided from the main power source to the product input wiring terminals or supplied power cable.

**DO NOT** operate the product in an explosive atmosphere or in the presence of flammable gases or fumes.

For continued protection against fire, replace the line fuse(s) only with the fuse(s) of the same voltage and current rating and type. **DO NOT** use repaired fuses or short-circuited fuse holders.

**Keep away from live circuits:** Operating personnel must not remove equipment covers or shields. Procedures involving the removal of covers or shields are for use by service-trained personnel only. Under certain conditions, dangerous voltages may exist even with the equipment switched off. To avoid dangerous electrical shock, **DO NOT** perform procedures involving cover or shield removal unless you are qualified to do so.

**DO NOT operate damaged equipment:** Whenever it is possible that the safety protection features built into this product have been impaired, either through physical damage, excessive moisture, or any other reason, REMOVE POWER and do not use the product until safe operation can be verified by service-trained personnel. If necessary, return the product to Hewlett-Packard Sales and Service Office for service and repair to ensure that safety features are maintained.

**Do not** service or adjust alone: Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

**Do not substitute parts or modify equipment:** Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification to the product. Return the product to a Hewlett-Packard Sales and Service Office for service and repair to ensure that safety features are maintained.

Rev. A

The information in this chapter provides an overview of flash RAM programming concepts. Read this chapter if you are unfamiliar with using automatic test equipment to program flash devices.

This chapter describes:

- Flash Programming Concepts, on page 1-3

- Flash Programming Tasks, on page 1-4

- Embedded Programming Algorithms for Flash Devices, on page 1-5

- The Advantages and Limitations of On-board Programming, on page 1-13

### 1.1 Flash RAM and On-board Programming

Flash RAM is a high-density, read-write, non-volatile memory source used in many electronics applications, such as digital cameras, modems, automotive engines, personal computers, and cellular phones. Unlike ROM, Flash memory is non-volatile, meaning data bits are retained even after removing the power supply. Additionally, flash memory is electrically erasable and re-writable in-system.

The utilization of flash memory devices by electronics manufacturers is on the rise. By the year 2000, the market for flash RAM is estimated to grow to \$10 billion. For many manufacturers, flash RAM is becoming a standard element of circuit board design. Attributes such as in-system programmability and non-volatility make flash memory products a flexible, low cost, reliable memory solution for an increasingly diverse range of electronic products.

The value of using flash RAM over other programmable logic devices is that data can be electrically erased and re-programmed insystem. When choosing a manufacturing process for writing data to flash memory devices, project management teams should consider flash related manufacturing issues that impact product profitability. Inventory control procedures, the availability of third party vendors who can meet just-in-time goals, and the cost of acquiring special tools if Small Outline Packages (**SOP**s) are in the board design are important considerations. These issues add to the complexity of designing boards that include flash technology.

With the miniaturization of flash devices, traditional flash programming methods have become slow and expensive to implement. Manufacturers that program flash devices on PROM programmers often encounter damage rates as high as two percent because of the extra handling steps required to install the smaller, more fragile devices. Automatic test equipment (ATE) can be effectively utilized for flash on-board programming (OBP) to reduce costs and improve test development speed.

HP 3070 systems with Flash70 software can used for on-board programming of flash memory devices. This guide contains information about the procedures, tasks, and syntax required to perform flash programming with HP 3070 test systems. If flash programming is a new technology for you, then you should read this chapter, if you are familiar with flash technology, read about design for on-board programming requirements in **Chapter 2**, "**Design For On-board Programming.**"

### 1.2 Flash Programming Concepts

You should be aware of the following concepts for programming flash memory devices:

- Flash memory is non-volatile.

- Flash memory is electrically erasable and writable.

- Non-blank flash devices must be erased prior to programming.

- Newer flash devices contain automated program verification procedures which reduce manual programming time and effort.

- Standardized libraries and algorithms can be used for programming flash devices.

Flash memory is a non-volatile, electrically erasable and writable memory originally developed by  $Intel_{\textcircled{m}}$  Corporation. Automatic programming modes in newer flash devices mean that flash algorithms are simpler and faster to implement. Like EPROM, flash memory devices must be erased before programming. HP Flash70 software manages flash programming activities at in circuit test, such as device erasure, verification and programming.

Programing methods for flash RAM vary based on part specifications and manufacturing requirements. **CFI**, the Common Flash Interface specification, enables the use of software algorithms for entire families of devices. CFI allows standardized software drivers to identify and use a variety of flash products because device identification data is embedded into the chip. Device identification data defines memory size, byte/word configuration, block configuration, and the voltages and timing information necessary for programming the device.

A variety of algorithms for programming flash devices exist.  $Intel_{\textcircled{B}}$  and Advanced Micro Devices  $(AMD_{\textcircled{B}})$  have developed the algorithms most commonly used for flash RAM programming. Other manufacturers generally follow these industry leaders.

Automatic on-chip verification methods simplify the flash programming process and result in more reliable programming. Newer flash devices have internal automatic program verification processes. These devices manage data verification procedures by automatically verifying the threshold levels of the data stored in the data cells. This increases testing efficiency because programmers no longer need to create separate threshold algorithms for every version of a flash device.

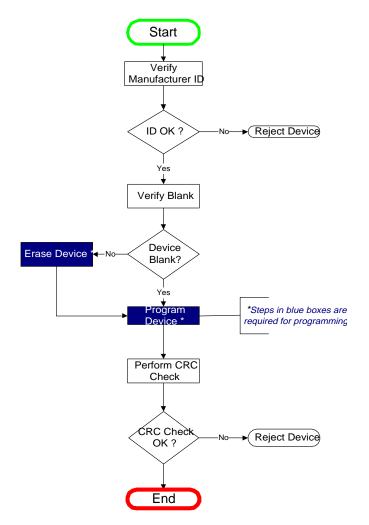

### 1.3 Flash Programming Tasks

Whether you are programming flash on-board with **ATE** or by some other method, the flash device programming process remains the same. In most test production environments, there are three steps:

#### 1. Device Identification

Identify the flash device by the manufacturer identification number.

The flash programming mechanism reads the manufacturer identification number from the device to ensure the correct device is ready for programming.

#### 2. Device Erasuref

Verify that the device is blank. If not, perform device erasure.

Flash devices must be blank before programming. New parts are shipped blank, but previously programmed parts must be erased prior to programming. Erasing a part changes all memory spaces on the flash device to a one state "1". This is necessary because the "program" command cannot program zero states to one.

Ensuring that flash devices are blank before programming is one of the most overlooked steps for test developers.

#### 3. Device Programming

Program the flash device with valid information stored in a hex data record file.

Flash devices are typically programmed with hex data records that follow either the  $Intel_{\textcircled{B}}$  Hex or  $Motorola_{\textcircled{B}}$  S-Record formats. Other formats exist, but they are not considered industry standards.

### 1.4 Embedded Programming Algorithms for Flash Devices

When 12.0 V flash memories were first introduced, cumbersome programming sequences were required to program and erase flash devices. To simplify the process, system software designers embedded flash programming algorithms onto newer flash devices. Embedded programming algorithms initialize, write, and read programming sequences automatically. In the HP 3070 environment, embedded algorithms are activated by the appropriate sequence of Vector Control Language (VCL) execute statements.

The two leading manufacturers of flash devices,  $Intel_{\ensuremath{\mathbb{R}}}$  and  $AMD_{\ensuremath{\mathbb{R}}}$ , use similar embedded programming algorithms. Flow charts that describe the write sequence algorithms follow. The procedures required to program a single byte of memory are indicated by the blocks in the diagram.

#### 1.4.1 Intel<sub>®</sub> Algorithms

Intel<sub>®</sub> has developed algorithms designed to work with Intel<sub>®</sub> flash device architecture. Intel<sub>®</sub> flash devices contain a Command User Interface (CUI), which serves as the interface between the microprocessor and the internal operation of a flash device. Command sequences written to the CUI initiate embedded algorithms on flash devices. Valid command sequences cause an on-chip Write State Machine (WSM) to execute the algorithms and timing required to perform operations such as *Block Erase* and *Byte / Word Program*. The Write State Machine on the flash device manages block erase, program and lock-bit configuration functions.

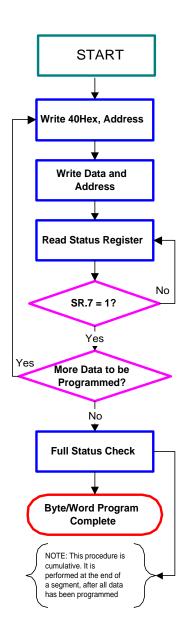

### 1.4.2 Intel® Automated Byte/Word Programming Algorithm

Flash device programming can be executed with the  $Intel_{\textcircled{B}} Byte/Word Program$  command. This involves writing two command sequences to the CUI: the Program Setup command (40H) and the address and data to be programmed. The Write State Machine then programs the data at specified address locations and verifies that programming was successful. When programmed, specified bits in an address location are changed to "0". The following flowchart illustrates the sequence of events that occur when the Byte/Word Program algorithm is executed.

#### 1.4.2.1 Intel<sub>®</sub> Byte/Word Programming Flowchart

- 1. Write 40H, Address: 40H is a write command for byte/word program setup. This command instructs the CUI to initialize the programming algorithm.

- 2. Write Address and Data: A second write command specifies the address and data to be written. The Write State Machine then controls program and program verify operations. Data is written to the cell and validated.

- 3. **Read Status Register:** The status register is read by writing the *Read Status Register* command. The status register determines when the program operation is completed successfully. After writing this command to the CUI, all subsequent read operations output data from the status register until another command is written to the CUI.

The contents of the status register are latched on the falling edge of the **OE** # or the first edge of **CE** #, whichever occurs last in the read cycle.

- 4. Verify Program Completion: The status register is used to check the Write State Machine Status pin ("SR.7") for the following conditions:

- If SR.7 = "0", the flash device is busy.

- If SR.7 = "1", the flash device program operation is complete and ready to receive more data.

- 5. Repeat steps 1 through 4, if there is more data.

- 6. **Perform Full Status Check:** A Full Status Check is performed after completing the device program operation.

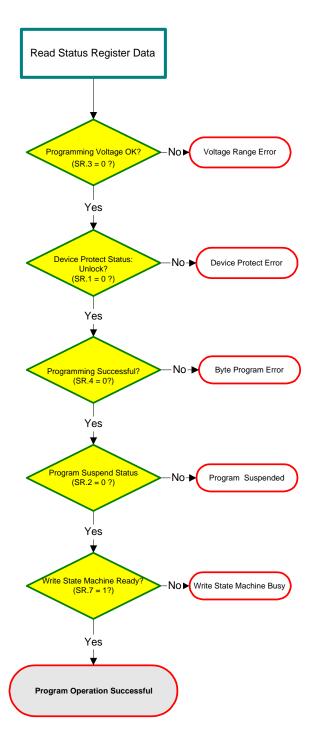

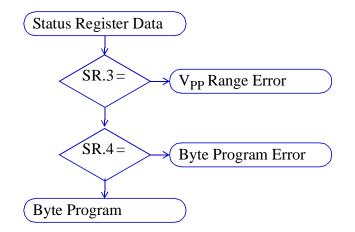

#### IIntel<sub>®</sub> Full Status Check Algorithm

In the HP 3070 environment, a full status check reads the following status register pins to validate the programming algorithm:

#### SR.3 = Programming Voltage Status

•If SR.3 = "1", low programming voltage is detected and the program operation aborts.

•If the SR.3 bit equals "0", the programming operation is successful.

#### **SR.1** = **Device Protect Status**

•If SR.1 ="1", a master lock-bit, block lock-bit and/or RP# lock is detected and the programming operation is aborted.

•If SR.1 = "0", this represents an unlocked bit.

#### SR.4 = Program and Set Lock-Bit Status

•If SR.4 = "1", an error in the Byte/Word programming occurred.

•If SR.4 = "0", the programming operation completed successfully:

#### SR.2 = Program Suspend Status

•If SR.2 = "1", the programming operation is suspended.

•If SR.2 = "0", the programming operation continues:

#### SR.7 = Write State Machine Status

•If SR.7 = "1", the Write State Machine is ready to program more data

•If SR.7 = "0", the Write State Machine is busy.

The status register check is cumulative, which means that if any program operation fails, an error occurs and the program operation is aborted. Thus, if 100,000 data locations have been programmed with one failing cell, the results will be reflected in the data register.

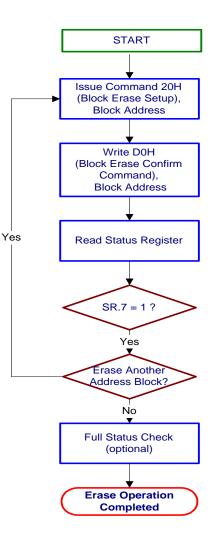

### 1.4.3 Intel<sub>®</sub> Block Erase Algorithm

Any non-blank flash device must be erased before it can be programmed. The Intel<sub>®</sub> Block Erase Algorithm performs and verifies device erasure. Block erasure is initiated by a two-cycle command sequence. To erase a block, issue the *Erase Setup* command (20H) and the *Erase Confirm* command (D0H) to the Command User Interface, along with the address of the block to be erased. Performing a block erase sets all bits within the block to "1". Only a single address block at a time can be erased. The flow chart illustrates how the Intel<sub>®</sub> Block Erase Algorithm works.

- 1. A two-cycle command sequence initiates the block erase procedure. First, write "20H", the *Erase Setup* command, to the CUI along with the address within the block to be erased.

- 2. Next, write "DOH", the *Erase Confirm* command, to the CUI, along with the address within the block to be erased. The erase operation does not begin until an Erase Confirm command has been issued. After this command is issued, the Write State Machine executes the following events within the device:

- Programs all bits within the block to "0".

- Verifies that all bits within the block are programmed.

- Erases all bits within the block by changing to "1".

- Verifies that all bits with the block are erased.

- 3. The Write State Machine Status pin, SR.7, is checked to determine if erasure is completed.

- If SR.7 = "1", the Write State Machine is ready and erasure is completed.

- If SR.7 = "0", the Write State Machine is busy.

- 4. If more address blocks are to be erased, repeat steps 1 to 3 until erase operation is completed.

### 1.5 AMD<sub>®</sub> Algorithms

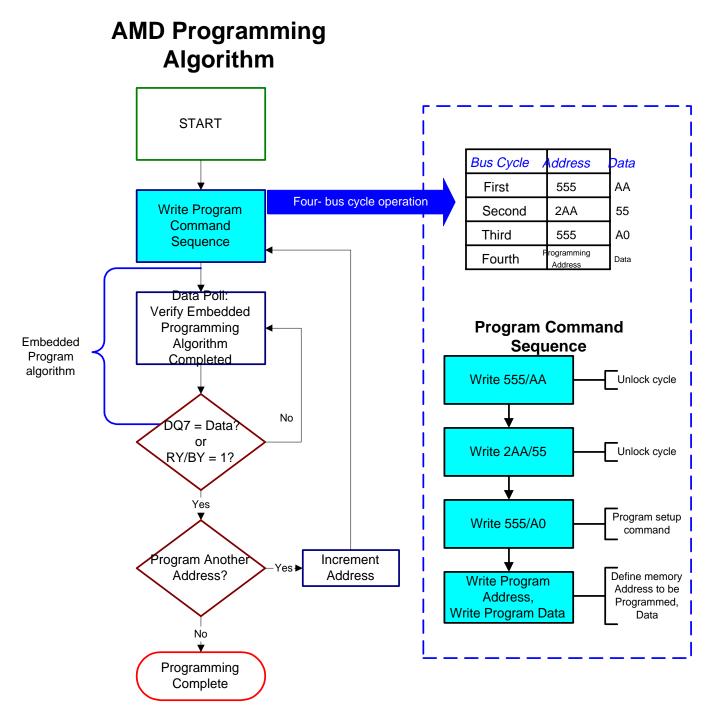

For  $AMD_{\textcircled{B}}$  compatible flash devices, the *command register* serves as the interface between a flash device and the microprocessor. An internal state machine uses the command register input to control device erasure and programming. Read and write device bus operations are initiated by writing commands to the command register. Device programming and erasure occur when the appropriate command sequence is written to the command register. For example, the *program command sequence* initiates the **Embedded Program** algorithm, which automatically performs device programming and verification functions. The *erase command sequence* initiates the **Embedded Erase** algorithm, which automatically preprograms the array and executes the erase operation. In order to write a command sequence for programming data or erasing sector addresses, the system must drive WE# (the Write Enable pin) and CE# (the Chip Enable pin) to low, and OE# (the Output Enable pin) to high. The Embedded Program algorithm and the Embedded Erase algorithm are presented in the following sections.

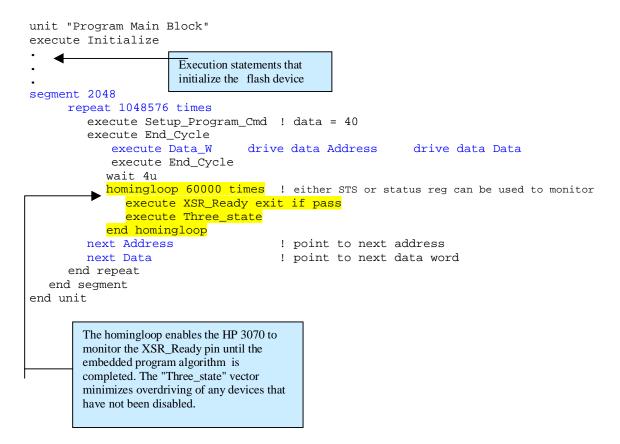

### 1.5.1 The AMD<sub>®</sub> Embedded Program Algorithm

AMD<sub>®</sub> compatible flash devices are programmed using the *program command sequence* to initiate the **Embedded Program** algorithm. The Embedded Program algorithm causes the device to automatically perform programming and program verification functions. To determine if the program operation is completed, the system reads the Data Polling bit (DQ7) or checks the Ready/ Busy (RY/BY#) status pin. If the RY/BY# pin equals "1" or DQ7 contains the data programmed to DQ7, programming has been completed. The device is then ready to accept another command or read data.

Programming is a four-bus-cycle operation initiated by the *byte program command sequence*. The corresponding bus-cycle operations are listed below:

- First bus-cycle: unlock write cycle

- Second bus-cycle: unlock write cycle

- Third bus-cycle: program set-up command

- Fourth bus-cycle: write to memory address location and write data at specified address

Addresses are latched on the falling edge of **WE #** or **CE #**, whichever happens last in the bus cycle. Data is latched on the rising edge of WE # or CE #, whichever happens first in the bus cycle. The rising edge of WE # or CE # begins the programming operation

Figure 1-1 AMD<sub>®</sub> Programming Algorithm

The AMD<sub>®</sub> Programming Algorithm flowchart shows the following sequence of commands and events:

- The writing of unlock commands such as 5555H/AAH, 2AAAH/55H and the program command 5555H/A0H is part of the command sequence that sets up the AMD<sub>®</sub> flash device for programming. The address and data to be programmed are written to the device. Pin "DQ7" goes to the opposite of its expected state while programming.

- 2. The automatic programming operation is completed when the Data Polling on pin "DQ7" is equal to the data written to this bit.

The RY/BY# pin indicates to the host system that the embedded algorithms are either in progress or completed. If the RY/BY# pin read is low, the device is busy with the program operation. If the output is high, the device is ready to accept additional read/ write operations.

3. After a sector is completely programmed, the address is incremented and new data is programmed.

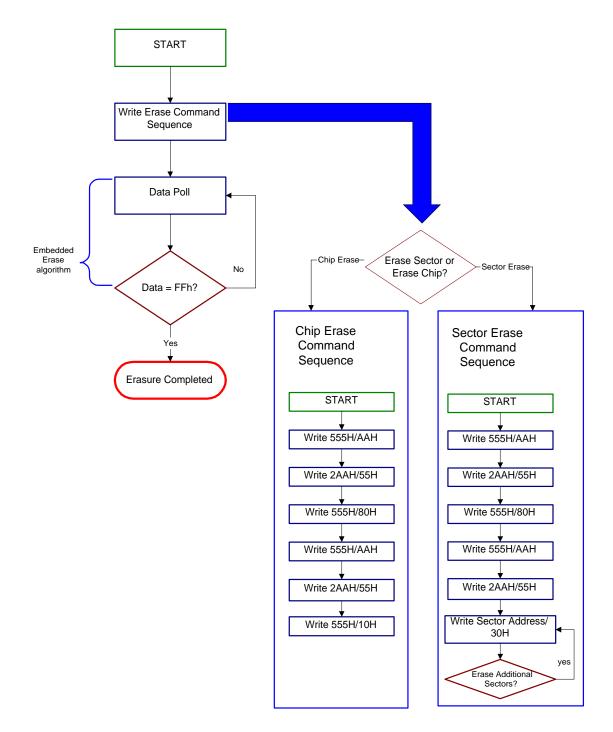

### 1.5.2 The AMD<sub>®</sub> Embedded Erase Algorithm

#### AMD® Erase Algorithm

Figure 1-2.  $AMD_{\mathbb{R}}$  Erase Algorithm

The erase command sequence is used to erase  $AMD_{\textcircled{B}}$  compatible flash devices. You can erase a single sector, multiple sectors, or the entire device. There are two common erase algorithms used for  $AMD_{\textcircled{B}}$  flash devices, Chip Erase, and Sector Erase. Each algorithm uses a six bus cycle operation. The following sequence of commands and events occurs with this algorithm:

- The erase sequences are initiated with two "unlock" bus cycles. The unlock cycles provide data protection against inadvertent writes.

- A "set-up" command is written to the command register.

- Two more "unlock" write cycles occur.

- Chip Erase: the *chip erase command* is written which triggers the Embedded Erase algorithm; or

- Sector Erase: the sector erase command consists of the address of the sector to be erased followed by the sector erase command 30H. This command can be repeated to erase multiple sectors.

- The Embedded Erase algorithm automatically pre-programs the entire memory or programs the sector and verifies that an all zero data pattern exists prior to erasure.

### 1.6 The Advantages and Limitations of On-board Programming

HP 3070 Series 3 hardware and software allows you to program flash memory devices at in-circuit test. There are several advantages and limitations to consider when determining whether to use on-board programming to program flash devices.

### 1.6.1 The Advantages of On-board Programming

### Cost reduction opportunities exist:

- ECOs are simpler to implement because flash programming can take as little as a day to set up. Once set up, code can be changed to accommodate new versions in minutes.

- There is no need for off-line programming. This can save between \$.40 and \$.60 per part.

• When the programming time of in-circuit tests (ICTs) is less than allotted throughput time for board test, the cost of ICT on-board programming is free.

Reduced handling can decrease the percentage of damaged parts:

- Flash devices are soldered to the PCB using surface mount assembly equipment. Reduced manual handling of components minimizes the potential for damaged or misaligned component pins.

- Additional handling equipment is not required for Small Outline Packages (SOPs).

- Automated component handling results in fewer bent component leads.

- Tape and reel media can be utilized for flash memory component installation.

### ✓ Hardware costs can decrease:

- There is no need to add flash memory sockets to the test boards.

- Combining flash programming with the in-circuit test process decreases total manufacturing expense.

Inventory control costs will decrease significantly:

- On-board programming of flash memory eliminates the need to assign additional part numbers to programmed devices.

- No individual device labeling is necessary because automated test equipment reads the part identification off the device.

- No inventory storage is required for programmed flash devices.

### 1.6.2 Limitations of On-board Programming:

Designing for OBP can increase hardware costs slightly:

- Additional circuitry that can three-state outputs of any components connected to flash devices is recommended to prevent damage to parts from excessive backdriving.

- Additional circuitry is recommended to prevent signal conflicts and bus contention.

- A full compliment of test land pads are needed for ATE programming unless slower methods such as JTAG Test Access Ports are used.

### **X** Test evaluation methods may need revision:

• Manufacturing line test throughput time increases by the amount of time it takes to program flash devices. Flash programming time varies from five to sixty seconds.

# Board test developers assume a more significant role in the early stages of projects.

- Since functionality is added to boards by programming flash devices at test time, board designers should plan for the testing process by communicating closely with test developers. This modifies the quality assurance role traditionally performed by test developers to more of a developmental role in the board development cycle.

- Faulty ICT program tests cannot be skipped without manufacturing process modifications.

Rev. A

This chapter requires an understanding of the flash programming concepts described in:

• Chapter 1, "Introduction to Flash Programming"

This chapter describes:

- On Board Programming, on page 2-2..

- Planning for Flash On-board Programming, on page 2-3.

- On-board Programming Design Considerations, on page 2-3.

- Board Design Recommendations, on page 2-4.

- What Test Developers Need to Know, on page 2-7.

- What is a Flash Programming Test?, on page 2-7.

- Data Sources and Board Topologies Effect OBP, on page 2-8.

- Board Topologies for On-board Programming, on page 2-9.

- Creating a Sample Design Document, on page 2-12.

### 2.1 On Board Programming

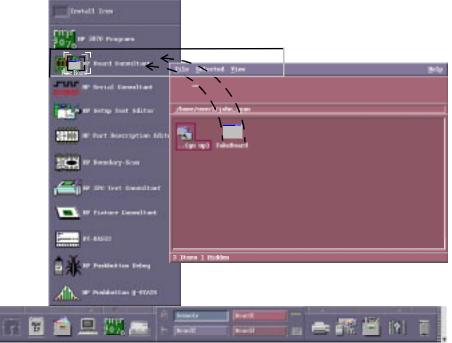

On-board programming utilizes automated test equipment to program flash memory devices that are installed on a printed circuit board. HP 3070 system hardware and software can be used to program flash devices on-board. Programming flash devices onboard in the production phase of board test development involves tasks almost identical to those currently utilized by HP 3070 test developers. However there are additional design consideration that should be incorporated into an effective on-board programming strategy. After learning some on-board programming fundamentals, programming flash devices in-circuit is no more complex than developing tests for other devices.

To simplify flash test development, HP 3070 systems provide digital libraries for many common flash devices. These digital libraries use standard Vector Control Language (VCL). If an exact match for your device is not found in the library, it is easy to create a custom test. Simply search the libraries for flash devices similar to those installed on your test board and make minor modifications to the library test. Then the standard flash library will work with the flash device under test.

NOTE

Although not required to perform flash programming, **Flash70** can be utilized to dramatically increase the speed of flash programming.

### 2.1.1 OBP: A Different Approach to Test Development

Successful OBP requires a different approach to test development. Traditionally, the testing phase of the board development process has played a quality assurance role in manufacturing. When programming flash devices on-board, the testing phase assumes a more significant role in the developmental stages of projects. For instance, software version control is managed by the test developer and board designers need to ensure that the board meets the test developers' requirements for OBP. Also, functionality is added to flash devices during production.

With on-board programming, design-for-testability should be emphasized. For best results, board designers should work collaboratively with test developers to incorporate testing conditions into the board design. Implementing OBP of flash memory with a design-for-testability approach can ultimately increase the profitability of most board design projects.

### 2.2 Planning for Flash On-board Programming

Planning is essential for quickly and easily implementing flash programming at in-circuit test time. Special design criteria for OBP should be added to the standard design criteria. It is necessary to plan board designs that allow the safe programming of devices and to provide sufficient information about data structures and data sources to the test programmers. To attain the maximum value from flash technology, design teams should create boards that can be programmed in-circuit, on-board, or by an in-circuit test, if required.

### 2.2.1 On-board Programming Design Considerations

The following design conditions are recommended for flash onboard programming:

- Adequate probe access to all flash device pins is needed, especially if 16 bit data is used for OBP.

- Circuitry that **prevents signal conflicts or bus contention** during OBP should be incorporated into the board design.

- ♦ An on-board voltage regulator should be used to ensure that V<sub>PP</sub> and V<sub>CC</sub> voltages used at test development work within the thresholds of in-system voltage specifications.

NOTE

Inaccurate programming can be caused by voltage differences between flash device  $V_{PP}$  requirements and the on-board power supply. Provide flash device specifications to board designers so that this problem can be addressed in the board design process.

• Designing a board so an on-board processor can program flash memories does not guarantee that the board can be programmed successfully in ICT.

If the flash device is being driven by another in-circuit device, it is unlikely that the **ATE** will program the device properly since the processor programs the part.

ICT usually backdrives output from upstream devices to perform cluster tests. The HP 3070 protects these devices against excessive backdriving with the Safeguard Protection feature. However, using the safeguard feature for flash OBP slows the process down to an unacceptable speed. To

effectively program flash devices, the HP 3070 safeguard feature must be turned off.

The ability to three-state upstream devices is essential for OBP. The only way to protect upstream devices is to incorporate three-stating mechanisms into the board design.

It takes between 2 and 45 seconds to program a flash device. Some studies have shown that devices can typically withstand backdriving for only a few milliseconds before damage results. Therefore, it is necessary to turn off the "safeguard" feature of the HP 3070 system. Since flash programming cannot be achieved in an acceptable time with safeguard on, three-stating devices on the board is the correct solution.

#### 2.2.2 Board Design Recommendations

#### 2.2.2.1 Disable Bi-directional Signals to Prevent Bus Conflicts

For digital testing, the capability to disable other devices on the bidirectional signals of the device under test is critical. The HP 3070 cannot program flash devices in-circuit unless all bi-directional pins on the data bus are disabled. Therefore, an important element of **OBP** design is the capability to quickly and easily disable the board's bidirectional signals with the automated test equipment. The best OBP board design utilizes a single input that can disable all parts directly accessing the memory to be programmed. This strategy enables more error free programming results. If this is not possible, it is important to supply test developers with disabling specifications for all ASICS and custom devices.

#### 2.2.2.2 Disable Input Signals to Prevent Backdriving Damage

Newer devices are more resilient to overdriving damage than those produced in earlier generations. Also, new HP 3070 programming libraries release backdriving signals more frequently within the test to limit backdriving time. However, board designers should provide isolation of all I/O pins on the device to be programmed to protect upstream devices from damage that might result from long periods of backdriving activity.

Disabling can be accomplished by three-stating devices. There are many methods to three-state devices for flash programming. Some of the most common **OBP** three-stating methods follow:

- Design ASICs with fully three-statable outputs. This eliminates the need for tests to overdrive the device's signals.

- Use volatile FPGAs, which power-up in a three-state condition.

- Add three-statable buffers to protect output. Commercial mpu are often difficult to disable. If the test developer disables mpu, the output signals are not likely to be three-stated along with the bidirectional signals.

- Use HP Boundary-Scan Interconnect Plus to three-state signals on BSDL compliant devices. HP Boundary-Scan Interconnect Plus automatically disables all I/Os on the device.

#### 2.2.2.3 Provide Access to All I/O Signals

Some board designs use only 8 bits of data on flash devices that can be operated in 8 or 16 data bit mode. Since flash devices can be programmed by word-wide methods, it is much more efficient to retain access to all device signals for ICT. In 16-bit cases, if the board design permits full access to all pins on the flash device, programming time can be reduced by almost 50 percent.

#### 2.2.2.4 Use System Power Supply Levels and Document Operational $V_{cc}$

Power and ground transient noise spikes are another source of OBP power supply problems. Board designers must address power, ground noise, and signal integrity issues in **OBP** environments. Pin drivers often route signals across long distances through **ATE** equipment which adds capacitance and inductance to the transmission line. By the time the programming voltage reaches the flash device under test, the signal integrity can degrade.

Utilize in-system power supply levels to gain the most reliable OBP results. This reduces the risk of inconsistent voltage applications, because the automatic write mechanism of some flash devices verifies the data content against thresholds relevant to the  $V_{CC}$  levels. If the  $V_{CC}$  level during programming is lower than it will be in the final product, data bits which verified as high during program verification may read below the high threshold during product operation.

If there is a voltage regulator present to generate  $V_{CC}$  during testing, then discrepancies in power supply levels disappear. When  $V_{CC}$  signals are provided directly from the HP 3070, the design team should document the operational  $V_{CC}$  level for the test team.

#### 2.2.2.5 Establish Direct Access to BSDL Signals

Devices that are compliant with IEEE 1149.1 standards can take advantage of Boundary-Scan technology to provide disabling. Boundary-Scan automates the disabling process via **BSDL**. Because most testing and programming of programmable logic is performed through the boundary-scan ports, having direct access to these signals and providing chains to interconnect them enhances the testability of the board. Designers need to supply accurate boundaryscan description files that operate properly with the devices on the board. The importance of Boundary-Scan for testing should be emphasized in on-board programming design plans.

#### 2.2.2.6 Provide Data Protection and Disabling Information

Most flash devices have programmatic protection capabilities against  $V_{PP}$  voltage so the board design does not need to be modified for **OBP**. Some older flash devices have data protection features which require that 12v be applied to address pins for erase and program operations. However, if the test program needs to apply 12 volts to an address line, buffers should be added to isolate  $V_{PP}$  from the address line to protect upstream devices from  $V_{PP}$  damage. When using this method, it is very important that the designer provides information to the manufacturing test team about how to disable access of the  $V_{CC}$  address lines when the program protection voltages are in use.

### 2.3 What Test Developers Need to Know

To generate successful flash programming tests, we recommend that test developers establish the following goals:

- Prepare a testing specification document for the designers of the board.

- Learn how to program devices with various types of data.

- Learn to verify that data is correctly programmed.

- Clear the data bus of all activity from other devices during programming. This is the most important element of the flash testing process with ATE.

In digital tests, interference from other devices can result in programming intermittence. Therefore, complete and easy disabling of upstream devices is essential for effective and safe **OBP**.

NOTE When upstream devices interfere with the programming of flash devices, the programming test may not fail. The data being programmed, however, will be incorrect. Adequate disabling prevents this type of problem.

Three-state all upstream devices which are exposed to backdriving. Although the "safeguard" feature of the HP 3070 provides protection from backdriving, safeguard must be turned off to achieve optimal programming times.

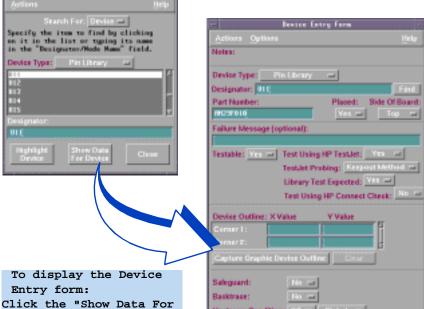

### 2.3.1 What is a Flash Programming Test?

Flash on-board programming tests are digital tests that use part libraries to actually program data onto an in-circuit flash device. Flash programming tests are simply digital "pin library" tests written in VCL. Typically, IPG generates six flash library tests during test development. The two tests required for flash **OBP** are "erase" and "program" (see **Flash Programming Tasks, on page 1-4)**.

Flash digital libraries contain information such as flash programming voltages (Vpp), in-system voltages (Vcc), and pin assignments. The **PDL** files included in the HP3070 B.3.00 software point to digital tests that program the most common flash devices on the market. The flash digital library models used for **OBP** testing are described more

completely in IPG, PDLs, and Flash Test Library Models, on page 6-11.

#### 2.3.2 Data Sources and Board Topologies Effect OBP

Choosing the best method to program flash devices in-circuit depends on several factors, including intended data sources and board topologies. It is important to understand the data sources provided and to make efficient use of them on various board topologies. Because flash devices and board topologies differ from project to project, knowledge of data structures and board topology is a very important **OBP** consideration.

For programming flash memory devices, HP 3070 systems support  $Intel_{\textcircled{B}}$  Hex,  $Motorola_{\textcircled{B}}$  S-Records, and decimal data source formats. Each flash device to be programmed requires a data source file. Understanding how to interpret these data formats enables you to compare the actual programmed data on a flash device to the expected data results.

For effective on-board programming design, it is important to understand the types of board topologies that enable faster programming methods. We recommend that board designers prepare documentation that defines the board topology and data source structures. Test developers can then use this documentation to develop effective test strategies.

# 2.3.3 Board Topologies for On-board Programming

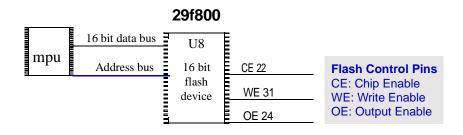

## 2.3.3.1 Individual Flash Devices Connected by Separate Data Busses

Test developers often work with boards that use separate data busses for each on-board flash device. This type of flash test is easy to implement because board designers typically provide one data file for programming. With one data file, the source usually matches the bit width of the flash devices on-board.

A diagram of this scenario follows:

16 bit full Access

Figure 2-1 OBP on 16 bit board topology

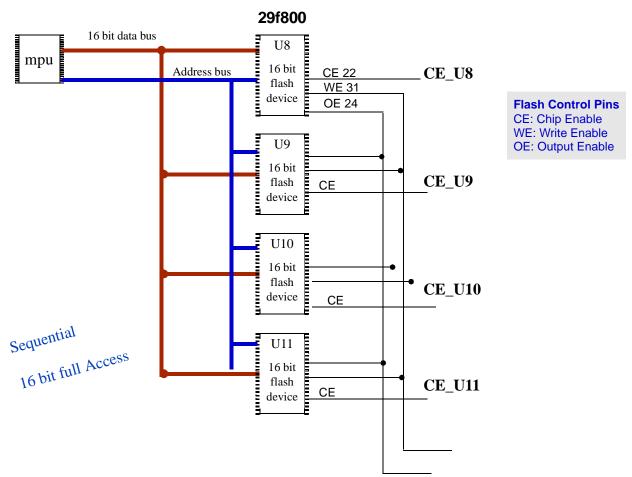

## 2.3.3.2 A Series of Flash Devices Connected to a Single Data Bus

Sometimes boards have many flash devices connected to a single data bus. Since all parts utilize the same data nodes, it is necessary to program the flash devices sequentially. With this type of design, **ATE** probes must have node access to the chip enable pins on all devices connected to the data bus. This enables each flash device to disable the others.

With this type of topology, the test program must ensure that the inputs to the other flash memories are disabled. In the topology depicted below, WE or OE lines are held in common. Each device has an independent chip enable. This means disabling can be automatically implemented by the HP 3070. The disable subroutine of the program test disables the appropriate parts.

The topology depicted below represents a series of flash devices connected by a single data bus.:

Figure 2-2 Multiple Devices and Single Data BusTopology

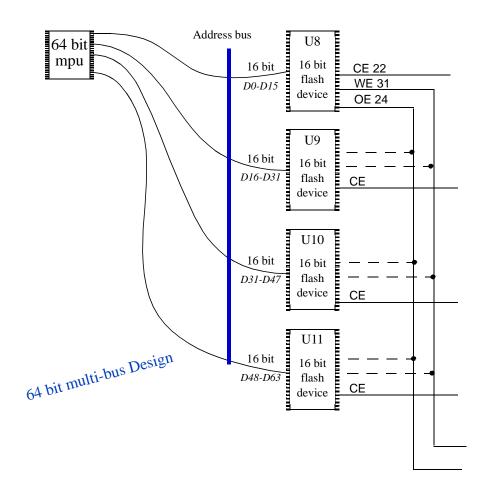

## 2.3.3.3 Multiple Flash Devices Connected to a Single Large Data Bus

Some board designs connect multiple flash devices to one large data bus. The example below shows a 64 bit mpu and four flash devices connected to separate data busses. This design is especially good for **OBP**, because disabling of other flash devices is not necessary. However, any peripheral devices connected to the flash device data bus must be disabled. Also, the HP 3070 is capable of programming all devices in parallel with a single cluster test to improve overall programming speed.

In this type of design, when separate nodes must be asserted to threestate upstream devices, these must be added to the program test.

A diagram of the topology follows:

Figure 2-3 Multiple Flash Devices on a Single Data Bus

## 2.3.3.4 Parallel Flash Programming With HP Throughput Multiplier

HP 3070 Throughput Multiplier is a software tool that can be used to perform Flash **OBP** parallel programming of identical boards. HP Throughput Multiplier allows you to program two or more boards of the same type and executes flash tests simultaneously on each board.

A diagram of this topology follows:

Figure 2-4 Flash OBP Parallell Programming Topology

## 2.3.4 Creating a Sample Design Document

We recommend that board designers and test developers create a flash programming design specification document. This document should include information about the flash devices to be programmed, board topology, address buses, data buses, and disabling information. An sample design document is shown next.

| Design Engineer:       Phone #:         Project Name:       FAX #:         Project Description:       FAX #: |  |

|--------------------------------------------------------------------------------------------------------------|--|

| Design Engineer:       Phone #:         Project Name:       FAX #:                                           |  |

| Design Engineer:       Phone #:         Project Name:       FAX #:                                           |  |

| Project Name: FAX #:                                                                                         |  |

| Project Name: FAX #:                                                                                         |  |

| Project Name: FAX #:                                                                                         |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

| Flash Device Type: Part Number                                                                               |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

| Board Topology Diagram (flash<br>devices, data bus, address bus,<br>control lines)                           |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

|                                                                                                              |  |

Rev. A

This chapter describes:

- What is a Flash Digital Test?, on page 3-2

- The Series 3 Flash Compiler, on page 3-2

- Flash70, on page 3-3

- Data Blocks, on page 3-11

# 3.1 What is a Flash Digital Test?

A flash test is a standard VCL digital test that uses an external data source to program a flash device. Unlike standard digital tests in which the data values are explicitly defined by internal vectors, flash digital tests program unpredictable data values from an external file. The external file is a formatted data record which provides the data the compiler uses to program the flash device. A programmer defined data structure called a data block specifies the external data source used to program the device. VCL statements within the data block define the external data file and how its data is interpreted. Dynamic vectors extract data and address information from the specified data file. The address and data are then applied to the device to be programmed within a data cycle created by standard VCL vectors. The compiler interprets the file and calculates the appropriate address to be applied with each byte of data.

Another difference between a standard digital test and a flash programming test is size. Flash tests are usually many times larger than standard digital tests. To accommodate the large size of flash device tests, flash data is programmed in smaller sections called segments which the HP 3070 treats as multiple test files. Any size data file can be programmed by one digital test by using a repeat loop that maximizes pin RAM, and directory and sequencer RAM usage for programming.

# 3.2 The Series 3 Flash Compiler

The Series 3 flash compiler is more efficient than earlier versions and works with  $Motorola_{\mathbb{R}}$  S-Records,  $Intel_{\mathbb{R}}$  Hex records, and integer data. Since most designers work with cross-compilers that generate  $Motorola_{\mathbb{R}}$  S-Records or  $Intel_{\mathbb{R}}$  Hex records, many new Flash70 features are optimized for these types of formatted data files.

## 3.2.1 Data Interpretation

The compiler parses the data and address sections of the formatted data records based on the definitions provided in the data block. Motorola<sub>®</sub> and Intel<sub>®</sub> record types contain a series of ASCII values representing bytes of data. How the compiler interprets the data from a formatted record depends on the cross-compiler used to generate the files and the device or devices to be programmed. Several user definable options are available to manage and define variances in data interpretation.

Options that can be defined within the data block include a **step modifier** and a **format modifier**. A step modifier is used to translate the address from the data file into an address that fits the pins of the device under test, as well as the board topology. Some cross-compilers and data file generators create data records in which the address is not incremented by each byte, but by each 16 bits of data. Thus, 16 or 32 bits of data are treated as one address location, rather than the expected single address per byte. The format modifier can be used to handle non-byte addressing in Intel<sub>®</sub> Hex and Motorola<sub>®</sub> S-Records.

## 3.2.2 Automatic Segment Removal

When the number of repeat loops or programming sequences is larger than the data source available, the compiler interprets data more efficiently. If the data is exhausted, the compiler does not execute unnecessary segments<sup>1</sup>. Segments must be programmed in their entirety. Thus, when data runs out before a segment has been completed, the compiler programs reverts to an end-of-data condition and programs "harmless" data, FF, to a single location. By default, this is the highest address in the device. Since this may not be the appropriate address for the data, the test programmer can define information in the data block to select the appropriate address location for the data to be programmed. Programming FF can result in many unnecessary programming sequences, increasing flash programming execution time. If FF data is distributed throughout a data file, the Series 3 compiler automatically removes these blocks of FF data. Several seconds may be saved by not programming this redundant data.

# 3.3 Flash70

Flash70 is an optional software product that improves flash programming time. Flash70 features include:

- Faster programming speed with the Flash70 algorithm:

- New library models to simplify flash test development.

- Comprehensive online documentation: the *Flash Programming Guide*

<sup>1.</sup> This may result in improved test times, depending on the size of the data source and the device to be programmed.

The Flash70 programming algorithm takes advantage of the new Control XT card's expanded memory. If you are not using Flash70, segment size is limited by the vector RAM behind the pins, which can never exceed 8k. With Flash70, segment size is determined by sequence RAM which is 1 MB on ControlXT cards. This larger size RAM increases the potential segment size for programming which improves flash programming speed.

## 3.3.1 The Flash70 Algorithm

The Flash70 algorithm improves programming speeds for flash devices. Significant improvements in Flash70 test speed are the result of decreased overhead for segment execution and more efficient use of expanded ControlXT memory.

To obtain the benefits of Flash70, you must purchase and enable Flash70 software. To enable the Flash70 algorithm, add the statement "enable flash70" in the board "config" file and include the keyword, "flash" in the VCL tests for your flash devices.

When Flash70 is used in combination with the flash compiler, dynamic vectors use the Flash70 algorithm for programming operations. This algorithm uses the faster, larger memory of the control card for all the variable data pointers. The slower pin card memory is used for data that doesn't need to be reloaded during the test. Thus, fewer segments are required to program a device.

## 3.3.2 Faster Tests with the Flash70 Algorithm

NOTE

It is not necessary to know the internal details the Flash70 algorithm to program flash devices. Read this section if you want to learn why the Flash70 algorithm is faster.

Flash70 utilizes an algorithm that improves the speed of programming flash devices. This improvement is the result of vector expansion. Vector expansion differs from the standard flash algorithm in the following way. With the standard flash compiler, pin RAM is used to store the combinations of ones and zeros needed to program data. Since pin RAM is only 8k, the time required to reload data becomes detrimental to flash programming performance. For example, a 35 pin address and data bus has 2<sup>35</sup> possible binary combinations to hold address and data information. Potentially, up to 34 Gigabits of information are needed to program the device. Theoretically, if the data file is perfectly random, the pin RAM must

be reloaded 4,000 times to program all the combinations (34Gb/8k = 4,000 Pin RAM reloads).

The Flash70 algorithm eliminates the time consuming need to reload pin RAM. Flash70 vector expansion divides the data into more easily managed chunks by programming eight to ten pins at a time. The pin RAM required to contain every combination for eight to ten pins is only  $2^8$  to  $2^{10}$  bits (i.e. 256 to 1024 combinations). Since the required memory is less than the 8K of pin RAM available, programming a device becomes a matter of loading the Pin RAM once with every combination possible for the smaller sections, and then using ControlXT Sequence RAM to organize the data.

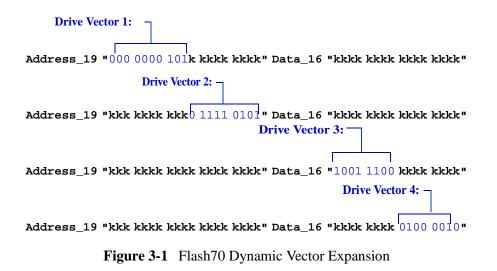

The Flash70 algorithm expands one vector into a multiple vector execution sequence. Some data records may require several vectors to implement programming completely, since multiple vectors are executed for one dynamic vector. The execution rate for the subvectors is 80ns per vector. In the example below, a single 160ns dynamic vector will become four 80ns vectors. The dynamic vector completes its cycle in 320ns while all other vectors operate at the user-selected vector cycle.

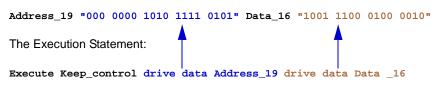

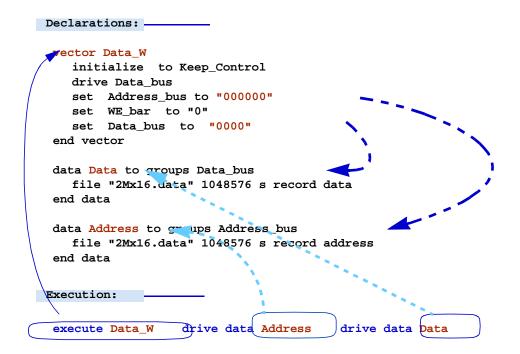

To better understand vector expansion, consider the following, drive only, example:

Data to be Programmed:

The execution statement above expands the address information to multiple vectors. *Keep\_control* specifies that the state of some of the pins from the previous sector remains unchanged. Each vector cycle changes only part of the data on the bus (between 8 to 10 bits). On the final vector cycle, the flash device receives the complete record.

Flash70 creates a four vector execution sequence from the single data record. In the example above, the execution sequence expands in the following order:

The Flash70 algorithm programs the entire device by transferring data records section by section to the data bus in the following order:

- 1. Drive Vector 1: 10 high order address bits.

- 2. Drive Vector 2: 9 low order address bits.

- 3. Drive Vector 3: 8 high order data bits.

- 4. Drive Vector 4: 8 low order data bits.

- 5. On the final write, **WE#** is asserted to program the entire address and data information to the flash device.

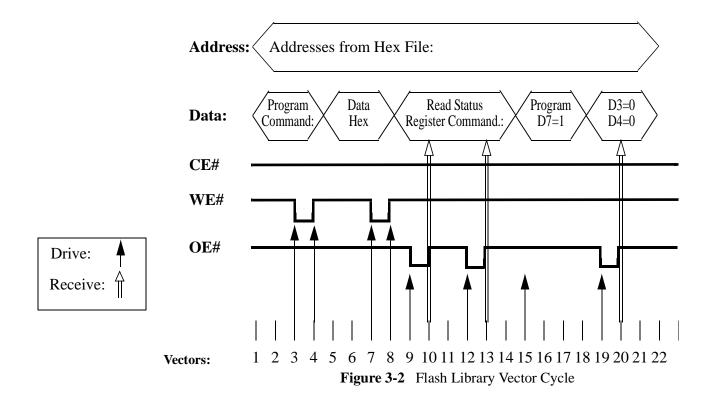

For example, WE# or **OE#** are offset from the expanded vector in which they are active, proportional to the user vectors. Final control lines are driven in the last vector to meet DUT requirements. Since there are no receives in this statement, the 6 MHz hybrid card receive limitations are not encountered.

Data read sequences depend on the multiple vector algorithm to create the vectors which comply with the 6 MHz hybrid card limitations. All control lines are driven in the second address vector. The **DUT** has at least one vector to settle its outputs before the receive vector is active. If more than one receive vector is executed, the only read receive is on the last vector.

Other notes concerning the Flash70 algorithm follow:

The receive delay should always be set to 100ns or less, when using a vector cycle of 160ns. The Flash70 compiler uses offsets for the receive delay. If the delay setting is greater

than 100ns, offsets cannot be used. In this case, the expanded vectors operate at the user defined vector speed.

- RAM behind the pins is loaded with fixed, static data.

- Sequence RAM dynamically controls the sequence of the data applied to pin RAM.

- The number of data and address pins on the data bus determines the quantity of vectors expanded. This process is controlled by the sequence RAM.

## 3.3.3 Obtaining 12MHz Speed on 6MHz cards

With Flash70, if you have double density 6 MHz hybrid cards in your system, it is possible to achieve additional improvement in programming speed. Flash70 enables some users to program at rates faster than the 160ns specification indicates. With good fixturing and fast memory, 80ns vector cycle time may be achievable. Since vector execution is very fast in flash programming, the faster cycling can improve programming performance significantly.

The 6 Mhz hybrid cards are unable to drive signals to a device and receive output is less than 160ns. The new Series 3 flash libraries are designed to drive and receive on different vectors to avoid violating the 6Mhz hybrid card specifications. The Flash70 compiler allows up to 80ns vector cycles when you override the board configuration to optimize overall programming times, even on 6Mhz cards.

**NOTE:** This diagram shows a standard programming sequence with the required device bus cycles. Observe the ICT drive and receive requirements. Note that the changes of inputs do not coincide with data receive vectors. This means that the test will never be required to change driven data and received data on the same vector. Since this is the case for programming tests, using 80ns vector cycles on a 6 Mhz system does not violate the specifications. This is why Flash70 allows you to override the system configuration. If you choose to override the system configuration on any test but the "program test", the specification will be violated and the test cannot be expected to operate.

The Flash70 algorithm can operate at up to 80ns vector cycles. Improving programming speed is a matter of trial and error. The flash programming libraries specify a vector cycling time that has been proven in the HP lab environment. This vector time, however, is not guaranteed, because the speed at which VCL tests can program depends heavily on fixturing. Efficient fixturing can reduce the time specified. The fastest vector cycle used cannot be less than 80ns.

To improve the speed of your flash programming, try these procedures:

1. Enable Flash70 in the board configuration file and VCL test

Index

files.

- Enter "enable flash70" in the board "config" file.

- At the beginning of the Declaration section, enter the "flash" statement in the "verify" and "program" test files for the **DUT**.

- 2. Before attempting to maximize the speed, make sure the device programs as expected based on the library definitions provided.

- 3. In the VCL test, reduce the vector cycle time to 80ns and the receive delay to less than 80ns.

For example, in the "program" test for the  $Intel_{\mathbb{R}}$  28f160, the following VCL statements appear:

vector cycle 160ns receive delay 100ns

In this case, you would change the vector cycle to 80ns and the receive delay to approximately 50ns.

NOTE The receive delay must always be less than the vector cycle time.

4. Compile and run the test on the device to be programmed.

- Either the flash device programs successfully, or

- If the flash device does not program successfully, increase the vector cycle and receive delay times until it does. In many cases, vector cycles can be faster than 160ns.

NOTE In rare cases, the vector cycle specified in the VCL test is too fast for reliable programming. If this occurs, the vector cycle time should be increased beyond the library recommendation.

## 3.3.4 Hardware Waits

A wait suspends execution of a VCL test and waits for a trigger before resuming. With the hardware wait, the triggering lines and states must be set up at the beginning of the VCL test, and cannot be changed during the test. During the wait, the drivers maintain their current states; however, the DUT clock, if any, continues to run (see *Digital-3*). Timed waits terminate at the end of a specified time. Other waits terminate when the specified triggering states are received.